# ELEC9704

Course Outline - Semester 1, 2016

**Never Stand Still**

**Faculty of Engineering**

School of Electrical Engineering and Telecommunications

# **Course Staff**

Course Convener: Prof. Chee Yee KWOK, Room 751 - Building E10

cy.kwok@unsw.edu.au

**Consultations:** You are encouraged to ask questions on the course material, during and after the lecture class times in the first instance, rather than via email. Lecturer consultation times will be advised during lectures. You are welcome to email the lecturer, who can answer your questions on this course and can also provide you with consultation times. ALL email enquiries should be made from your student email address with ELEC9704 in the subject line, otherwise they will not be answered.

**Keeping Informed:** Announcements may be made during classes, via email (to your student email address) and/or via online learning and teaching platforms – in this course, we will use Moodle <a href="https://moodle.telt.unsw.edu.au/login/index.php">https://moodle.telt.unsw.edu.au/login/index.php</a>. Please note that you will be deemed to have received this information, so you should take careful note of all announcements.

# **Course Summary**

This is a postgraduate course. The main focus of the subject is on semiconductor processes involved in the fabrication of very large scale silicon integrated circuits. Initially, the course will attempt to study individual processes, and towards the end these processes are integrated together into a process schedule for the fabrication of CMOS and bipolar VLSI circuits. Because integrated circuits fail from time to time, failure analysis plays an important role in process development. The course will include lectures on analytical techniques employed in understanding the causes of failure in order to modify the processes for better reliability.

VLSI technology is moving at a very rapid pace, spurred by the demand for further and further miniaturisation, greater circuit complexity and functionality per chip. Minimum feature sizes in production in '60s were tens of  $\mu m$ . In the '70s, it was several  $\mu m$ , in the '80s it was about 1 $\mu m$ , in the '90s it is submicron and now in the 21st century, it is the deep-deep-sub micron (<50nm range). Acronyms have evolved from SSI to MSI to LSI to VLSI to ULSI to GSI and now Terascale a head are enormous. In the past 20 years, 'ultimate' limits of scaling were predicted, and only to be surpassed years later. Wafer size of 300mm is now in production and will move to 450mm!!

The subject will enable students to have a broad grasp of the multi-disciplinary nature of the VLSI technology, bringing together the know-how of physicist, chemist, engineers and mathematicians. It will provide the basics for students, who may enter the semiconductor industry, to build on. It is an exciting field of research and we should count ourselves fortunate to be witnessing and participating in this era of unparalleled 'technology explosion'.

#### **Contact Hours**

This postgraduate course consists of 3 hours of lectures in the evenings. Problem discussions are included in the lectures and will not be treated as separate tutorials.

| Lectures | Day    | Time  | Location |

|----------|--------|-------|----------|

|          |        |       |          |

|          | Monday | 6-9pm | Rm 214   |

# Context and aims

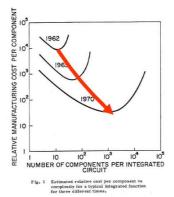

"Reduced cost is one of the big attractions of integrated electronics, and the cost advantage continues to increase as the technology evolves toward the production of larger and larger circuit functions on a single semiconductor substrate"

Electronics, Volume 38, No. 8, April 19, 1965

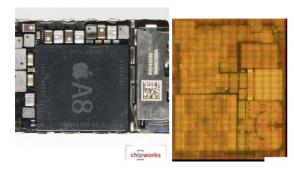

"The Apple A8 is, of course, the most interesting element in the new iPhone 6. All clues point to it being manufactured by TSNC on a 20nm node, and that makes it one of the first 20nm chips out there. The A8 is also some 13% smaller than last year's A7, while packing nearly double the amount of transistors – up from around 1 billion to some 2 billion transistors in the Apple A8. An yes, RAM is still 1GB on the iPhone". ITRS 2015 Paolo Report

The above examples gives us an amazing snapshot of how far the technology has moved over the last 50 years. The iPhone 6 is still fresh in our minds. All these would not have been possible if it were not for the advances in scaling of devices from tens of microns to tens of nanometers in today's technology. How is this possible? That is the subject of this course.

# Aims:

The course aims to familiarize students with silicon integrated technology and equip them with fundamental know-hows on which they build their future career in the semiconductor fabrication foundries and research areas.

# **Indicative Lecture Schedule**

| Period           | Lecture Topics                                                            | Due dates |

|------------------|---------------------------------------------------------------------------|-----------|

| Week 1<br>(29/2) | Introduction to VLSI Technology: historical perspective and trends today. |           |

| Week 2<br>(7/3)   | Silicon crystal growth and wafer preparation |                            |

|-------------------|----------------------------------------------|----------------------------|

| Week 3<br>(14/3)  | Oxidation of silicon                         |                            |

| Week 4<br>(21/3)  | Impurity diffusion in silicon                |                            |

|                   | Mid-session break (Easter)                   |                            |

| Week 5<br>(4/4)   | Ion implantation of impurities into silicon  | Mini-quiz-1                |

| Week 6<br>(11/4)  | Epitaxy growth on silicon substrates         |                            |

| Week 7<br>(18/4)  | Thin Film deposition techniques              | Assignment 1 due 18/4/2016 |

| Week 8<br>(25/4)  | Wet etching, Dry(plasma) etching             | Mini-quiz-2                |

| Week 9<br>(2/5)   | Lithography, Metallization                   |                            |

| Week 10<br>(9/5)  | VLSI process integration                     |                            |

| Week 11<br>(16/5) | 3D integration                               | Mini-quiz-3                |

| Week 12<br>(23/5) | Failure Analysis Techniques                  | Assignment 2 due 23/5/2016 |

| Week 13<br>(30/5) | Revision                                     |                            |

# **Assessment**

| 2 Assignments/project | 25% |

|-----------------------|-----|

| Mini-quizes           | 10% |

| Presentation          | 5%  |

| Final Exam (3 hours)  | 60% |

# **Course Details**

# **Credits**

This is a 6 UoC course and the expected workload is 10 hours per week throughout the 13 week semester.

# **Relationship to Other Courses**

This is a postgraduate course offered to students in the Master of Engineering Science at the University of New South Wales. The course complements the microelectronics design courses ELEC4602 and ELEC 9701. It lays the ground work for Microsystems Course ELEC 9703.

# **Pre-requisites and Assumed Knowledge**

There is no specific pre-requisite for the course. However, it suits to students who are familiar with semiconductor device and microelectronics design similar to the course covered in ELEC4603 and ELEC4602 in EE undergraduate program. It is further assumed that the students are familiar with some basic chemistry. The course is multidisciplinary in nature.

# **Learning outcomes**

After the successful completion of the course, the student will be able to:

- 1. Understand the basic process steps in making integrated circuits

- 2. Understand how these steps are integrated in the process

- 3. Understand the technology limitations of each process

- 4. Understand the impact of these limitations on the IC designer's options

- 5. Develop an appreciation of the technology trends

- 6. Work in a group to present a seminar on a topic not taught in class: to develop public presentation skills and expand knowledge base in the course.

This course is designed to provide the above learning outcomes which arise from targeted graduate capabilities listed in *Appendix A*. The targeted graduate capabilities broadly support the UNSW and Faculty of Engineering graduate capabilities (listed in *Appendix B*). This course also addresses the Engineers Australia (National Accreditation Body) Stage I competency standard as outlined in *Appendix C*.

# **Syllabus**

Introduction to VLSI Technology: historical perspective and trends today; Silicon crystal growth and wafer preparation; Oxidation of silicon; Impurity diffusion in silicon; Ion implantation of impurities into silicon; Epitaxy growth on silicon substrates; Thin Film deposition techniques; Wet etching, Dry(plasma) etching; Lithography, Metallization; VLSI process integration; 3D integration; Failure Analysis Techniques.

# **Teaching Strategies**

# **Delivery Mode**

The teaching in this course aims at establishing a good fundamental understanding of the areas covered using:

- Formal face-to-face lectures, which provide you with a focus on the core analytical material in the course, together with qualitative, alternative explanations to aid your understanding;

- There are no separate tutorials but done lectures from time to time. Some self-paced exercises will be given out in class during the course.

- Where possible, lectures will be videoed and uploaded to the school website for students to clarify specific aspects of the lecture. It is not a substitute for missed lectures.

# Learning in this course

You are expected to attend <u>all</u> lectures, and attempt assignments in order to maximise learning. In addition to the lecture notes/video, you should read relevant sections of the recommended reference text. Reading additional texts will further enhance your learning experience. Group learning is also encouraged. UNSW *assumes* that self-directed study of this kind is undertaken in addition to attending face-to-face classes throughout the course.

#### **Tutorial classes**

There are no separate tutorial classes.

# **Laboratory program**

There are no laboratory programs. However, a short lab tour of ANFF is arranged towards the later part of the course.

# **Assessment**

| 2 Assignments                    | 25% |

|----------------------------------|-----|

| Mini-quizes                      | 10% |

| Presentation                     | 5%  |

| Final Exam (3 hours closed book) | 60% |

- 1. <u>Mini-quizzes</u>: 5 mins quiz will be held in class fortnightly just before the lecture. It will start in week 3 and fortnightly from there on. The questions are not meant to be hard and students, who have been following the course, are expected to easily pass, and even score 100%. This is to encourage students to follow the course while rewarding them for doing so.

- 2. <u>Assignment:</u> There are also two compulsory written **assignments** for this course, which will be released on the course Moodle after Weeks 5 and 9 respectively. The assignments will each worth 10% of the overall mark in total for this course. It is expected that the students complete assignments on their own. Assignment submissions are set on Wednesdays in week 8 and 12 for each assignment respectively.

- 3. <u>Presentation</u>: there will be group presentations on various topics related to VLSI technology trends, new developments, approaches, and future challenges. The groups can choose other topics provided that they discuss them with the lecturer. The number of students in a group will be decided in week 2 or 3. Presentations will be held for 20min before the lecture in week 6, 8, and 11.

- 4. *Final exam*: there will be a closed book 3 hour final exam.

The assessment scheme in this course reflects the intention to assess your learning progress through the semester..

#### **Final Exam**

The exam in this course is an closed-book 3 hour written examination, comprising of four compulsory questions. University approved calculators are allowed. The examination tests analytical and critical thinking and general understanding of the course material in a controlled fashion. Questions may be drawn from any aspect of the course, unless specifically indicated otherwise by the lecturer. Marks will be assigned according to the correctness of the responses.

# **Relationship of Assessment Methods to Learning Outcomes**

|                      | Learning outcomes |   |   |   |   |   |  |

|----------------------|-------------------|---|---|---|---|---|--|

| Assessment           | 1                 | 2 | 3 | 4 | 5 | 6 |  |

|                      |                   |   |   |   |   |   |  |

| Assignment1          | Х                 | Х | Х |   |   |   |  |

| Assignment 2         | Х                 | Х | Х | Х | Х |   |  |

| Seminar Presentation |                   |   |   | Х | Х | Х |  |

| Mini-Quizes          | Х                 | Х | Х | Х |   |   |  |

| Final exam           | Х                 | Х | Х | Х | Х |   |  |

# **Course Resources**

#### **Textbooks**

The no textbook set for this course but a good reference book to buy is by JD Plummer. The following are the recommended reference books.

- 1. JD Plummer, MD Deal, PB Griffin, "Silicon VLSI Technology", Prentice Hall, 2000.

- 2. S K Ghandi, "VLSI Fabrication Principles", Wiley.

- 3. S M Sze, "VLSI Technology", McGraw-Hill.

- 4. S A Campbell, "The science and Engineering of Microelectronic Fabrication", Oxford University Press.

- 5. R A Levy, "Microelectronic Materials and Processes", Kluwer.

- 6. E H Nicollian and J R Brews, "MOS Physics and Technology", Wiley.

- 7. D K Schroder, "Semiconductor material and device characterisation", Wiley Interscience

#### **On-line resources**

#### Moodle

As a part of the teaching component, Moodle may be used to disseminate teaching materials, host forums and occasionally quizzes. Assessment marks will also be made available via Moodle: https://moodle.telt.unsw.edu.au/login/index.php.

# **Mailing list**

Announcements concerning course information will be given in the lectures and/or on Moodle and/or via email (which will be sent to your student email address).

# **Other Matters**

# **Academic Honesty and Plagiarism**

Plagiarism is the unacknowledged use of other people's work, including the copying of assignment works and laboratory results from other students. Plagiarism is considered a form of academic misconduct, and the University has very strict rules that include some severe penalties. For UNSW policies, penalties and information to help you avoid plagiarism, see <a href="http://www.lc.unsw.edu.au/plagiarism">http://www.lc.unsw.edu.au/plagiarism</a>. To find out if you understand plagiarism correctly, try this short quiz: <a href="https://student.unsw.edu.au/plagiarism-quiz">https://student.unsw.edu.au/plagiarism-quiz</a>.

# **Student Responsibilities and Conduct**

Students are expected to be familiar with and adhere to all UNSW policies (see <a href="https://my.unsw.edu.au/student/atoz/ABC.html">https://my.unsw.edu.au/student/atoz/ABC.html</a>), and particular attention is drawn to the following:

# Workload

It is expected that you will spend at least **ten to twelve hours per week** studying a 6 UoC course, from Week 1 until the final assessment, including both face-to-face classes and *independent*, *self-directed study*. In periods where you need to need to complete assignments or prepare for examinations, the workload may be greater. Over-commitment has been a common source of failure for many students. You should take the required

workload into account when planning how to balance study with employment and other activities.

#### **Attendance**

Regular and punctual attendance at all classes is expected. UNSW regulations state that if students attend less than 80% of scheduled classes they may be refused final assessment.

# **General Conduct and Behaviour**

Consideration and respect for the needs of your fellow students and teaching staff is an expectation. Conduct which unduly disrupts or interferes with a class is not acceptable and students may be asked to leave the class.

# **Work Health and Safety**

UNSW policy requires each person to work safely and responsibly, in order to avoid personal injury and to protect the safety of others.

# **Special Consideration and Supplementary Examinations**

You must submit all assignments and attend all examinations scheduled for your course. You should seek assistance early if you suffer illness or misadventure which affects your course progress. All applications for special consideration must be **lodged online through myUNSW within 3 working days of the assessment**, not to course or school staff. For more detail, consult https://my.unsw.edu.au/student/atoz/SpecialConsideration.html.

# **Continual Course Improvement**

This course is under constant revision in order to improve the learning outcomes for all students. Please forward any feedback (positive or negative) on the course to the course convener or via the Course and Teaching Evaluation and Improvement Process. You can also provide feedback to ELSOC who will raise your concerns at student focus group meetings. As a result of previous feedback obtained for this course and in our efforts to provide a rich and meaningful learning experience, we have continued to evaluate and modify our delivery and assessment methods.

#### **Administrative Matters**

On issues and procedures regarding such matters as special needs, equity and diversity, occupational health and safety, enrolment, rights, and general expectations of students, please refer to the School and UNSW policies:

http://www.engineering.unsw.edu.au/electrical-engineering/policies-and-procedureshttps://my.unsw.edu.au/student/atoz/ABC.html

# **Appendix A: Targeted Graduate Capabilities**

Electrical Engineering and Telecommunications programs are designed to address the following targeted capabilities which were developed by the school in conjunction with the requirements of professional and industry bodies:

- The ability to apply knowledge of basic science and fundamental technologies:

- The skills to communicate effectively, not only with engineers but also with the wider community;

- The capability to undertake challenging analysis and design problems and find optimal solutions;

- Expertise in decomposing a problem into its constituent parts, and in defining the scope of each part;

- A working knowledge of how to locate required information and use information resources to their maximum advantage;

- Proficiency in developing and implementing project plans, investigating alternative solutions, and critically evaluating differing strategies;

- An understanding of the social, cultural and global responsibilities of the professional engineer;

- The ability to work effectively as an individual or in a team;

- An understanding of professional and ethical responsibilities;

- The ability to engage in lifelong independent and reflective learning.

# **Appendix B: UNSW Graduate Capabilities**

The course delivery methods and course content directly or indirectly addresses a number of core UNSW graduate capabilities, as follows:

- Developing scholars who have a deep understanding of their discipline, through lectures and solution of analytical problems in tutorials and assessed by assignments and written examinations.

- Developing rigorous analysis, critique, and reflection, and ability to apply knowledge and skills to solving problems. These will be achieved by the laboratory experiments and interactive checkpoint assessments and lab exams during the labs.

- Developing capable independent and collaborative enquiry, through a series of tutorials spanning the duration of the course.

- Developing independent, self-directed professionals who are enterprising, innovative, creative and responsive to change, through challenging design and project tasks.

# **Appendix C: Engineers Australia (EA) Professional Engineer Competency Standard**

|                         | Program Intended Learning Outcomes                                                                    |          |

|-------------------------|-------------------------------------------------------------------------------------------------------|----------|

|                         | PE1.1 Comprehensive, theory-based understanding of underpinning fundamentals                          | <b>✓</b> |

| Knowledge<br>Skill Base | PE1.2 Conceptual understanding of underpinning maths, analysis, statistics, computing                 | <b>√</b> |

| y οί<br>Σ ∐             | PE1.3 In-depth understanding of specialist bodies of knowledge                                        | <b>√</b> |

| 7 1S                    | PE1.4 Discernment of knowledge development and research directions                                    |          |

| PE1:<br>and             | PE1.5 Knowledge of engineering design practice                                                        | <b>√</b> |

| <u></u>                 | PE1.6 Understanding of scope, principles, norms, accountabilities of sustainable engineering practice |          |

| 4 a a -                 | PE2.1 Application of established engineering methods to complex problem                               | <b>√</b> |

|                                               | solving                                                                                          |          |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------|----------|

|                                               | PE2.2 Fluent application of engineering techniques, tools and resources                          | <b>√</b> |

|                                               | PE2.3 Application of systematic engineering synthesis and design processes                       | <b>√</b> |

|                                               | PE2.4 Application of systematic approaches to the conduct and management of engineering projects | <b>√</b> |

| =                                             | PE3.1 Ethical conduct and professional accountability                                            |          |

| :3: Professiona<br>and Personal<br>Attributes | PE3.2 Effective oral and written communication (professional and lay domains)                    | <b>√</b> |

| ofes<br>ers<br>but                            | PE3.3 Creative, innovative and pro-active demeanour                                              | <b>✓</b> |

| ן פ ⊾                                         | PE3.4 Professional use and management of information                                             | <b>√</b> |

| PE3:<br>an                                    | PE3.5 Orderly management of self, and professional conduct                                       |          |

| <b>_</b>                                      | PE3.6 Effective team membership and team leadership                                              | <b>√</b> |